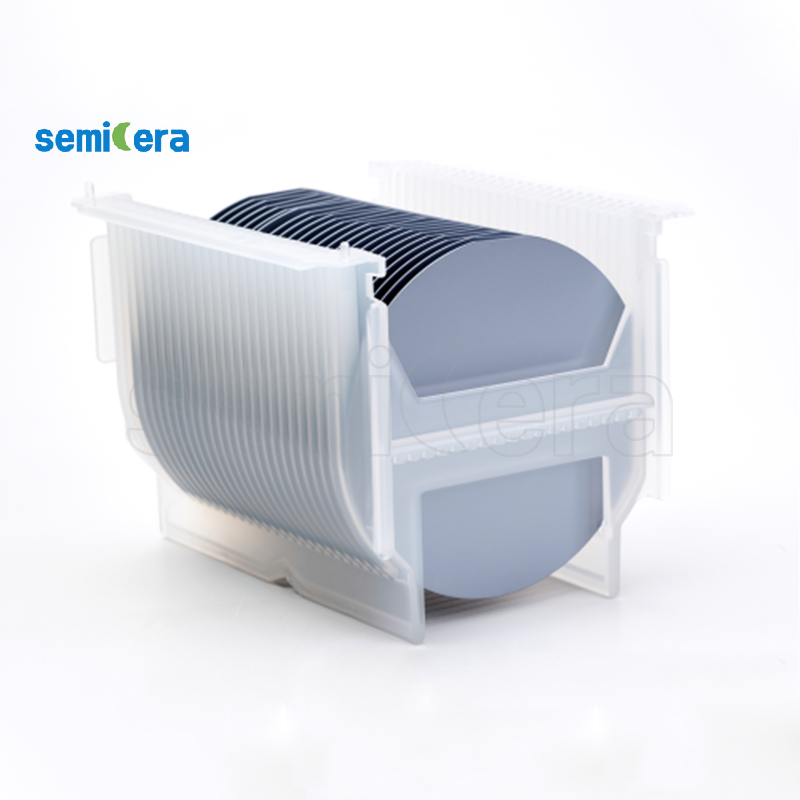

Semiceraພູມໃຈສະເໜີຂອງຕົນ4" ແຜ່ນຍ່ອຍ Gallium Oxide, ເປັນວັດສະດຸກໍ່ສ້າງພື້ນຖານທີ່ສ້າງຂຶ້ນເພື່ອຕອບສະຫນອງຄວາມຕ້ອງການທີ່ເພີ່ມຂຶ້ນຂອງອຸປະກອນ semiconductor ປະສິດທິພາບສູງ. Gallium Oxide (ກ2O3) substrates ສະເຫນີ bandgap ultra-wide, ເຮັດໃຫ້ມັນເຫມາະສົມສໍາລັບການຜະລິດເອເລັກໂຕຣນິກພະລັງງານການຜະລິດຕໍ່ໄປ, UV optoelectronics, ແລະອຸປະກອນຄວາມຖີ່ສູງ.

ຄຸນນະສົມບັດທີ່ສໍາຄັນ:

• Ultra-Wide Bandgap: ໄດ້4" ແຜ່ນຍ່ອຍ Gallium Oxideມີຊ່ອງຫວ່າງປະມານ 4.8 eV, ອະນຸຍາດໃຫ້ມີການຍົກເວັ້ນແຮງດັນແລະຄວາມທົນທານຕໍ່ອຸນຫະພູມ, ມີປະສິດທິພາບດີກວ່າວັດສະດຸ semiconductor ແບບດັ້ງເດີມເຊັ່ນຊິລິຄອນ.

•ແຮງດັນໄຟຟ້າສູງ: substrates ເຫຼົ່ານີ້ເຮັດໃຫ້ອຸປະກອນສາມາດດໍາເນີນການຢູ່ທີ່ແຮງດັນແລະພະລັງງານທີ່ສູງຂຶ້ນ, ເຮັດໃຫ້ມັນສົມບູນແບບສໍາລັບຄໍາຮ້ອງສະຫມັກທີ່ມີແຮງດັນສູງໃນເອເລັກໂຕຣນິກພະລັງງານ.

•ຄວາມໝັ້ນຄົງດ້ານຄວາມຮ້ອນສູງ: ແຜ່ນຍ່ອຍ Gallium Oxide ສະຫນອງການນໍາຄວາມຮ້ອນທີ່ດີເລີດ, ຮັບປະກັນການປະຕິບັດທີ່ຫມັ້ນຄົງພາຍໃຕ້ເງື່ອນໄຂທີ່ຮຸນແຮງ, ເຫມາະສໍາລັບການນໍາໃຊ້ໃນສະພາບແວດລ້ອມທີ່ຕ້ອງການ.

•ຄຸນນະພາບວັດສະດຸສູງ: ດ້ວຍຄວາມຫນາແຫນ້ນຂອງຂໍ້ບົກພ່ອງຕ່ໍາແລະຄຸນນະພາບຂອງຜລຶກສູງ, ຊັ້ນຍ່ອຍເຫຼົ່ານີ້ຮັບປະກັນການປະຕິບັດທີ່ຫນ້າເຊື່ອຖືແລະສອດຄ່ອງ, ເພີ່ມປະສິດທິພາບແລະຄວາມທົນທານຂອງອຸປະກອນຂອງທ່ານ.

•ຄໍາຮ້ອງສະຫມັກອະເນກປະສົງ: ເຫມາະສໍາລັບການນໍາໃຊ້ທີ່ຫຼາກຫຼາຍ, ລວມທັງ transistors ພະລັງງານ, diodes Schottky, ແລະອຸປະກອນ UV-C LED, ເຮັດໃຫ້ການປະດິດສ້າງທັງໃນພາກສະຫນາມພະລັງງານແລະ optoelectronic.

ສຳຫຼວດອະນາຄົດຂອງເທັກໂນໂລຢີ semiconductor ດ້ວຍ Semicera's4" ແຜ່ນຍ່ອຍ Gallium Oxide. substrates ຂອງພວກເຮົາຖືກອອກແບບມາເພື່ອສະຫນັບສະຫນູນຄໍາຮ້ອງສະຫມັກທີ່ກ້າວຫນ້າທາງດ້ານຫຼາຍທີ່ສຸດ, ສະຫນອງຄວາມຫນ້າເຊື່ອຖືແລະປະສິດທິພາບທີ່ຈໍາເປັນສໍາລັບອຸປະກອນທີ່ທັນສະໄຫມຂອງມື້ນີ້. ໄວ້ວາງໃຈ Semicera ສໍາລັບຄຸນນະພາບແລະນະວັດກໍາໃນວັດສະດຸ semiconductor ຂອງທ່ານ.

| ລາຍການ | ການຜະລິດ | ຄົ້ນຄ້ວາ | Dummy |

| ພາລາມິເຕີ Crystal | |||

| Polytype | 4H | ||

| ການວາງທິດທາງພື້ນຜິວຜິດພາດ | <11-20 >4±0.15° | ||

| ຕົວກໍານົດການໄຟຟ້າ | |||

| ຝຸ່ນ | n-ປະເພດໄນໂຕຣເຈນ | ||

| ຄວາມຕ້ານທານ | 0.015-0.025ohm·ຊມ | ||

| ຕົວກໍານົດການກົນຈັກ | |||

| ເສັ້ນຜ່າສູນກາງ | 150.0±0.2ມມ | ||

| ຄວາມຫນາ | 350 ± 25 ມມ | ||

| ປະຖົມນິເທດຮາບພຽງ | [1-100]±5° | ||

| ຄວາມຍາວຮາບພຽງຂັ້ນຕົ້ນ | 47.5±1.5ມມ | ||

| ຮາບພຽງຮອງ | ບໍ່ມີ | ||

| TTV | ≤5ມມ | ≤10ມມ | ≤15ມມ |

| LTV | ≤3ມມ(5ມມ*5ມມ) | ≤5ມມ(5ມມ*5ມມ) | ≤10ມມ(5ມມ*5ມມ) |

| ກົ້ມຫົວ | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Warp | ≤35ມມ | ≤45ມມ | ≤55ມມ |

| ຄວາມຫຍາບດ້ານໜ້າ (AFM) | Ra≤0.2nm (5μm*5μm) | ||

| ໂຄງສ້າງ | |||

| ຄວາມຫນາແຫນ້ນຂອງ micropipe | <1 ea/cm2 | <10 ea/cm2 | <15 ea/cm2 |

| ຄວາມເປື້ອນຂອງໂລຫະ | ≤5E10ອະຕອມ/ຊມ2 | NA | |

| BPD | ≤1500 ea/cm2 | ≤3000 ea/cm2 | NA |

| TSD | ≤500 ea/cm2 | ≤1000 ea/cm2 | NA |

| ຄຸນະພາບດ້ານຫນ້າ | |||

| ດ້ານໜ້າ | Si | ||

| ສໍາເລັດຮູບ | Si-face CMP | ||

| ອະນຸພາກ | ≤60ea/wafer (ຂະຫນາດ≥0.3μm) | NA | |

| ຮອຍຂີດຂ່ວນ | ≤5ea/ມມ. ຄວາມຍາວສະສົມ ≤ ເສັ້ນຜ່າສູນກາງ | ຄວາມຍາວສະສົມ≤2*ເສັ້ນຜ່າສູນກາງ | NA |

| ເປືອກສີສົ້ມ/ຂຸມ/ຮອຍເປື້ອນ/ຮອຍຂີດຂ່ວນ/ຮອຍແຕກ/ການປົນເປື້ອນ | ບໍ່ມີ | NA | |

| ຊິບຂອບ/ຫຍໍ້ໜ້າ/ຮອຍແຕກ/ແຜ່ນ hex | ບໍ່ມີ | ||

| ພື້ນທີ່ Polytype | ບໍ່ມີ | ພື້ນທີ່ສະສົມ≤20% | ພື້ນທີ່ສະສົມ≤30% |

| ເຄື່ອງຫມາຍເລເຊີດ້ານຫນ້າ | ບໍ່ມີ | ||

| ຄຸນະພາບກັບຄືນໄປບ່ອນ | |||

| ກັບຄືນໄປບ່ອນສໍາເລັດຮູບ | C-face CMP | ||

| ຮອຍຂີດຂ່ວນ | ≤5ea/mm, ຄວາມຍາວສະສົມ≤2*ເສັ້ນຜ່າສູນກາງ | NA | |

| ຂໍ້ບົກພ່ອງດ້ານຫຼັງ (ຊິບຂອບ/ຫຍໍ້ໜ້າ) | ບໍ່ມີ | ||

| ກັບຄືນໄປບ່ອນ roughness | Ra≤0.2nm (5μm*5μm) | ||

| ເຄື່ອງໝາຍເລເຊີກັບຄືນ | 1 ມມ (ຈາກຂອບເທິງ) | ||

| ຂອບ | |||

| ຂອບ | Chamfer | ||

| ການຫຸ້ມຫໍ່ | |||

| ການຫຸ້ມຫໍ່ | Epi-ພ້ອມດ້ວຍການຫຸ້ມຫໍ່ສູນຍາກາດ ການຫຸ້ມຫໍ່ cassette ຫຼາຍ wafer | ||

| * ຫມາຍເຫດ: "NA" ຫມາຍຄວາມວ່າບໍ່ມີຄໍາຮ້ອງຂໍລາຍການທີ່ບໍ່ໄດ້ກ່າວເຖິງອາດຈະຫມາຍເຖິງ SEMI-STD. | |||