ອຸປະກອນພະລັງງານ Semiconductor ຄອບຄອງຕໍາແຫນ່ງຫຼັກໃນລະບົບເອເລັກໂຕຣນິກພະລັງງານ, ໂດຍສະເພາະໃນແງ່ຂອງການພັດທະນາຢ່າງໄວວາຂອງເຕັກໂນໂລຢີເຊັ່ນ: ປັນຍາປະດິດ, ການສື່ສານ 5G ແລະຍານພາຫະນະພະລັງງານໃຫມ່, ຄວາມຕ້ອງການດ້ານການປະຕິບັດຂອງພວກເຂົາໄດ້ຮັບການປັບປຸງ.

ຊິລິໂຄນຄາໄບ(4H-SiC) ໄດ້ກາຍເປັນວັດສະດຸທີ່ເຫມາະສົມສໍາລັບການຜະລິດອຸປະກອນໄຟຟ້າ semiconductor ປະສິດທິພາບສູງເນື່ອງຈາກຂໍ້ໄດ້ປຽບຂອງມັນເຊັ່ນ bandgap ກ້ວາງ, ການນໍາຄວາມຮ້ອນສູງ, ຄວາມເຂັ້ມແຂງພາກສະຫນາມ breakdown ສູງ, ອັດຕາການອີ່ມຕົວຂອງ drift ສູງ, ສະຖຽນລະພາບທາງເຄມີແລະການຕໍ່ຕ້ານລັງສີ. ຢ່າງໃດກໍຕາມ, 4H-SiC ມີຄວາມແຂງສູງ, brittleness ສູງ, inertness ສານເຄມີທີ່ເຂັ້ມແຂງ, ແລະຄວາມຫຍຸ້ງຍາກໃນການປຸງແຕ່ງສູງ. ຄຸນນະພາບຂອງພື້ນຜິວຂອງ wafer substrate ຂອງມັນແມ່ນສໍາຄັນສໍາລັບຄໍາຮ້ອງສະຫມັກອຸປະກອນຂະຫນາດໃຫຍ່.

ດັ່ງນັ້ນ, ການປັບປຸງຄຸນນະພາບພື້ນຜິວຂອງ wafers substrate 4H-SiC, ໂດຍສະເພາະແມ່ນການເອົາຊັ້ນທີ່ເສຍຫາຍຢູ່ເທິງຫນ້າການປຸງແຕ່ງ wafer, ແມ່ນກຸນແຈເພື່ອບັນລຸການປຸງແຕ່ງ wafer ຊັ້ນນໍາ 4H-SiC ທີ່ມີປະສິດທິພາບ, ການສູນເສຍຕ່ໍາແລະມີຄຸນນະພາບສູງ.

ການທົດລອງ

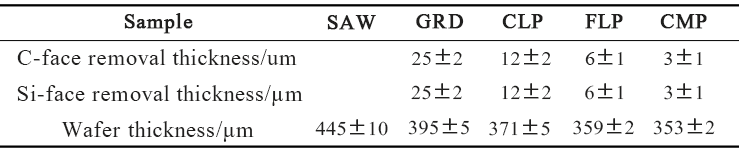

ການທົດລອງໃຊ້ ingot N-type 4H-SiC ຂະຫນາດ 4 ນິ້ວທີ່ປູກໂດຍວິທີການຂົນສົ່ງ vapor ທາງກາຍະພາບ, ເຊິ່ງຖືກປຸງແຕ່ງໂດຍຜ່ານການຕັດສາຍ, ການຂັດ, ການຂັດທີ່ຫຍາບຄາຍ, ການຂັດແລະການຂັດລະອຽດ, ແລະບັນທຶກຄວາມຫນາຂອງການໂຍກຍ້າຍຂອງຫນ້າ C ແລະຫນ້າ Si. ແລະຄວາມຫນາຂອງ wafer ສຸດທ້າຍໃນແຕ່ລະຂະບວນການ.

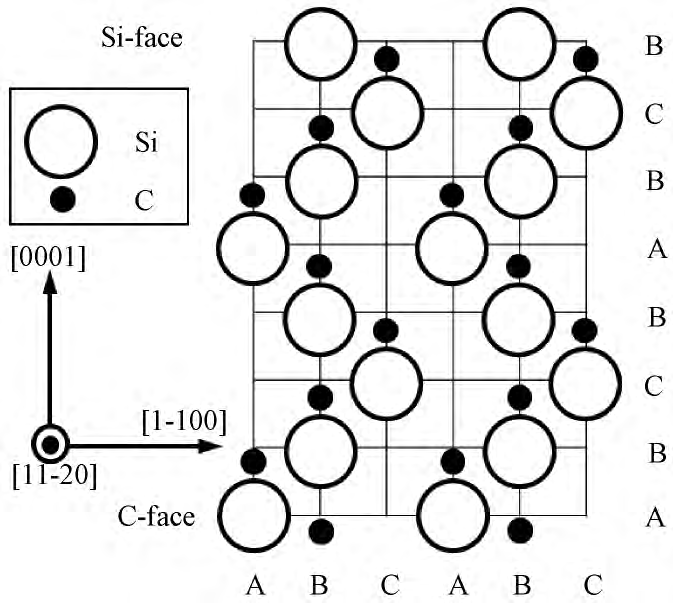

ຮູບທີ 1 ແຜນວາດແຜນຜັງຂອງໂຄງສ້າງຜລຶກ 4H-SiC

ຮູບທີ 2 ຄວາມຫນາທີ່ຖອດອອກຈາກ C-side ແລະ Si-side ຂອງ 4H-SiC waferຫຼັງຈາກຂັ້ນຕອນການປຸງແຕ່ງທີ່ແຕກຕ່າງກັນແລະຄວາມຫນາຂອງ wafer ຫຼັງຈາກການປຸງແຕ່ງ

ຄວາມຫນາ, ຮູບຮ່າງຂອງພື້ນຜິວ, ຄວາມຫຍາບແລະຄຸນສົມບັດກົນຈັກຂອງ wafer ໄດ້ຖືກສະແດງຢ່າງເຕັມສ່ວນໂດຍເຄື່ອງທົດສອບພາລາມິເຕີເລຂາຄະນິດຂອງ wafer, ກ້ອງຈຸລະທັດການລົບກວນທີ່ແຕກຕ່າງກັນ, ກ້ອງຈຸລະທັດຜົນບັງຄັບໃຊ້ປະລໍາມະນູ, ເຄື່ອງມືວັດແທກຄວາມຫນາແຫນ້ນຂອງພື້ນຜິວແລະ nanoindenter. ນອກຈາກນັ້ນ, ຄວາມລະອຽດສູງ X-ray diffractometer ໄດ້ຖືກນໍາໃຊ້ເພື່ອປະເມີນຄຸນນະພາບຂອງໄປເຊຍກັນຂອງ wafer.

ຂັ້ນຕອນການທົດລອງແລະວິທີການທົດສອບເຫຼົ່ານີ້ສະຫນອງການສະຫນັບສະຫນູນດ້ານວິຊາການຢ່າງລະອຽດສໍາລັບການສຶກສາອັດຕາການໂຍກຍ້າຍວັດສະດຸແລະຄຸນນະພາບຫນ້າດິນໃນລະຫວ່າງການປຸງແຕ່ງ 4H-SiC wafers.

ໂດຍຜ່ານການທົດລອງ, ນັກຄົ້ນຄວ້າໄດ້ວິເຄາະການປ່ຽນແປງຂອງອັດຕາການໂຍກຍ້າຍວັດສະດຸ (MRR), morphology ດ້ານຫນ້າແລະ roughness, ເຊັ່ນດຽວກັນກັບຄຸນສົມບັດກົນຈັກແລະຄຸນນະພາບໄປເຊຍກັນຂອງ 4H-.SiC wafersໃນຂັ້ນຕອນການປຸງແຕ່ງທີ່ແຕກຕ່າງກັນ (ການຕັດສາຍ, ການຂັດ, ການຂັດຫຍາບ, ການຂັດດີ, ການຂັດ).

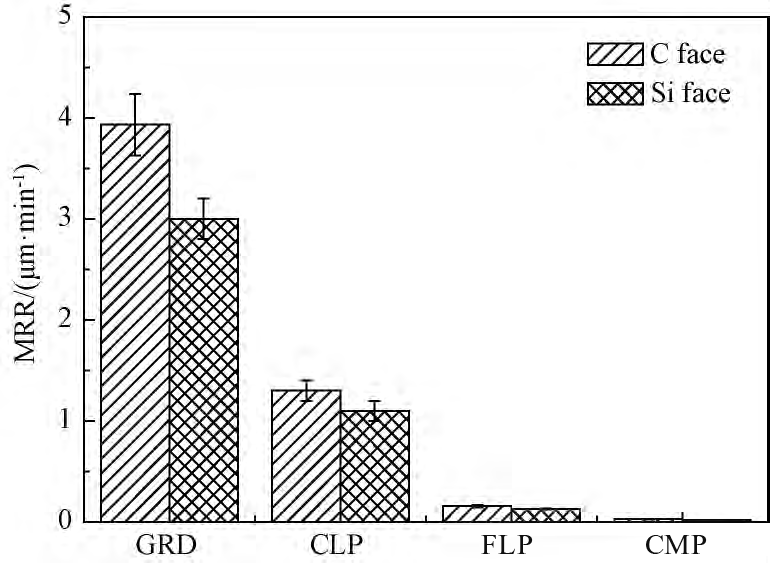

ຮູບທີ 3 ອັດຕາການກໍາຈັດວັດສະດຸຂອງ C-face ແລະ Si-face ຂອງ 4H-SiC waferໃນຂັ້ນຕອນການປຸງແຕ່ງທີ່ແຕກຕ່າງກັນ

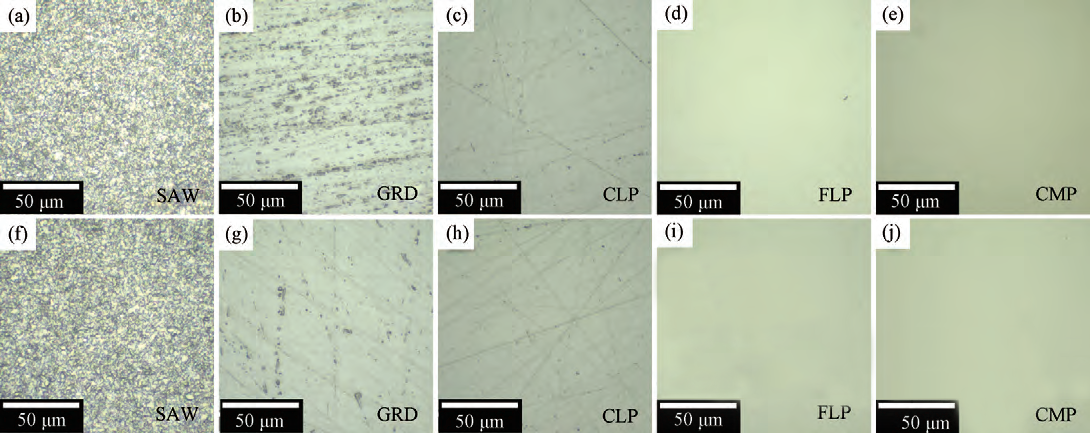

ການສຶກສາໄດ້ພົບເຫັນວ່າເນື່ອງຈາກ anisotropy ຂອງຄຸນສົມບັດກົນຈັກຂອງໃບຫນ້າໄປເຊຍກັນທີ່ແຕກຕ່າງກັນຂອງ 4H-SiC, ມີຄວາມແຕກຕ່າງກັນໃນ MRR ລະຫວ່າງ C-face ແລະ Si-face ພາຍໃຕ້ຂະບວນການດຽວກັນ, ແລະ MRR ຂອງ C-face ແມ່ນສູງກວ່າຢ່າງຫຼວງຫຼາຍ. ຂອງ Si-face. ດ້ວຍຄວາມກ້າວຫນ້າຂອງຂັ້ນຕອນການປຸງແຕ່ງ, ຮູບຮ່າງຂອງຫນ້າດິນແລະຄວາມຫຍາບຄາຍຂອງ wafers 4H-SiC ຖືກປັບປຸງໃຫ້ດີຂຶ້ນເທື່ອລະກ້າວ. ຫຼັງຈາກຂັດ, Ra ຂອງ C-face ແມ່ນ 0.24nm, ແລະ Ra ຂອງ Si-face ຮອດ 0.14nm, ເຊິ່ງສາມາດຕອບສະຫນອງຄວາມຕ້ອງການຂອງການເຕີບໂຕຂອງ epitaxial.

ຮູບທີ 4 ຮູບພາບກ້ອງຈຸລະທັດທາງແສງຂອງພື້ນຜິວ C (a~e) ແລະ Si (f~j) ຂອງ 4H-SiC wafer ຫຼັງຈາກຂັ້ນຕອນການປຸງແຕ່ງທີ່ແຕກຕ່າງກັນ

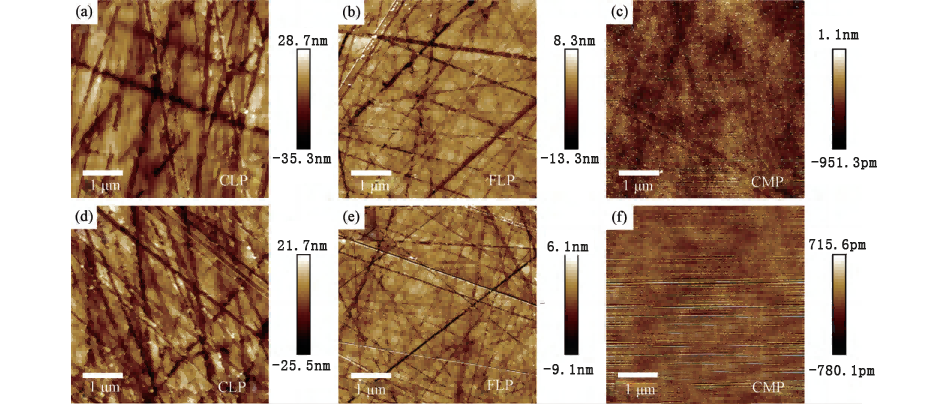

ຮູບທີ 5 ຮູບພາບກ້ອງຈຸລະທັດກຳລັງປະລໍາມະນູຂອງພື້ນຜິວ C (a~c) ແລະ Si (d~f) ຂອງ 4H-SiC wafer ຫຼັງຈາກຂັ້ນຕອນການປຸງແຕ່ງ CLP, FLP ແລະ CMP

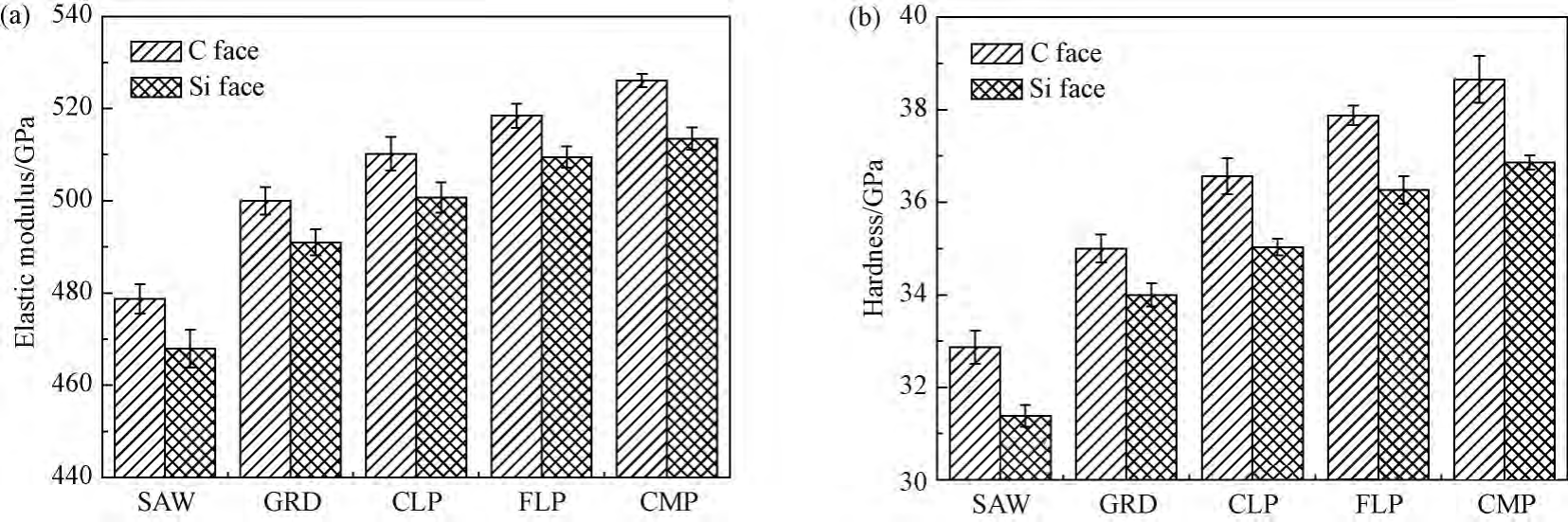

ຮູບ 6 (a) ໂມດູລ elastic ແລະ (b) ຄວາມແຂງຂອງຫນ້າດິນ C ແລະ Si ຂອງ wafer 4H-SiC ຫຼັງຈາກຂັ້ນຕອນການປຸງແຕ່ງທີ່ແຕກຕ່າງກັນ

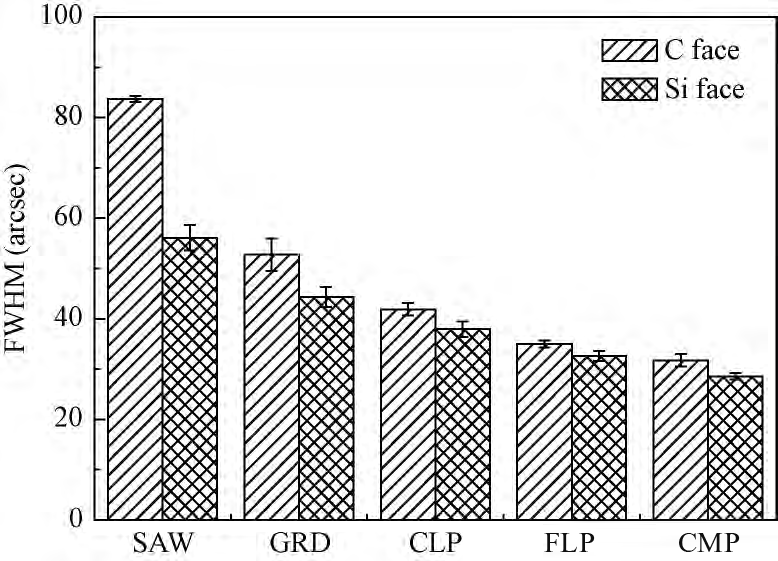

ການທົດສອບຄຸນສົມບັດກົນຈັກສະແດງໃຫ້ເຫັນວ່າຫນ້າ C ຂອງ wafer ມີຄວາມທົນທານບໍ່ດີກ່ວາວັດສະດຸດ້ານ Si, ລະດັບການແຕກຫັກຂອງ brittle ຫຼາຍກວ່າໃນລະຫວ່າງການປຸງແຕ່ງ, ການໂຍກຍ້າຍວັດສະດຸໄວ, ແລະ morphology ດ້ານຫນ້າຂ້ອນຂ້າງບໍ່ດີແລະ roughness. ການເອົາຊັ້ນທີ່ເສຍຫາຍຢູ່ເທິງຫນ້າດິນທີ່ຖືກປຸງແຕ່ງແມ່ນກຸນແຈສໍາຄັນໃນການປັບປຸງຄຸນນະພາບຂອງຫນ້າດິນຂອງ wafer. ຄວາມກວ້າງເຄິ່ງຄວາມສູງຂອງເສັ້ນໂຄ້ງ rocking 4H-SiC (0004) ສາມາດຖືກນໍາໃຊ້ເພື່ອກໍານົດລັກສະນະ intuitively ແລະຢ່າງຖືກຕ້ອງແລະການວິເຄາະຊັ້ນຄວາມເສຍຫາຍຂອງຫນ້າດິນຂອງ wafer ໄດ້.

ຮູບທີ່ 7 (0004) ເສັ້ນໂຄ້ງ rocking ເຄິ່ງກວ້າງຂອງ C-face ແລະ Si-face ຂອງ 4H-SiC wafer ຫຼັງຈາກຂັ້ນຕອນການປຸງແຕ່ງທີ່ແຕກຕ່າງກັນ

ຜົນໄດ້ຮັບການຄົ້ນຄວ້າສະແດງໃຫ້ເຫັນວ່າຊັ້ນຄວາມເສຍຫາຍຂອງຫນ້າດິນຂອງ wafer ສາມາດຖືກໂຍກຍ້າຍອອກເທື່ອລະກ້າວຫຼັງຈາກການປຸງແຕ່ງ wafer 4H-SiC, ເຊິ່ງປັບປຸງຄຸນນະພາບຫນ້າດິນຂອງ wafer ໄດ້ຢ່າງມີປະສິດທິພາບແລະສະຫນອງການອ້າງອິງດ້ານວິຊາການສໍາລັບການປຸງແຕ່ງທີ່ມີປະສິດທິພາບສູງ, ການສູນເສຍຕ່ໍາແລະມີຄຸນນະພາບສູງ. ຂອງ 4H-SiC substrate wafers.

ນັກຄົ້ນຄວ້າໄດ້ປຸງແຕ່ງ wafers 4H-SiC ໂດຍຜ່ານຂັ້ນຕອນການປຸງແຕ່ງທີ່ແຕກຕ່າງກັນເຊັ່ນ: ຕັດສາຍ, ການຂັດ, ການຂັດຫຍາບ, ການຂັດແລະການຂັດ, ແລະໄດ້ສຶກສາຜົນກະທົບຂອງຂະບວນການເຫຼົ່ານີ້ຕໍ່ຄຸນນະພາບຂອງຫນ້າດິນຂອງ wafer.

ຜົນໄດ້ຮັບສະແດງໃຫ້ເຫັນວ່າດ້ວຍຄວາມກ້າວຫນ້າຂອງຂັ້ນຕອນການປຸງແຕ່ງ, morphology ດ້ານແລະ roughness ຂອງ wafer ໄດ້ຖືກປັບໃຫ້ເຫມາະເທື່ອລະກ້າວ. ຫຼັງຈາກການຂັດ, ຄວາມຫຍາບຂອງ C-face ແລະ Si-face ຮອດ 0.24nm ແລະ 0.14nm ຕາມລໍາດັບ, ເຊິ່ງຕອບສະຫນອງຄວາມຕ້ອງການຂອງການເຕີບໂຕຂອງ epitaxial. C-face ຂອງ wafer ມີຄວາມເຄັ່ງຄັດທີ່ບໍ່ດີກວ່າວັດສະດຸ Si-face, ແລະມີຄວາມສ່ຽງຕໍ່ການແຕກຫັກຂອງ brittle ໃນລະຫວ່າງການປຸງແຕ່ງ, ເຊິ່ງກໍ່ໃຫ້ເກີດສະພາບຜິວທີ່ຂ້ອນຂ້າງບໍ່ດີແລະຄວາມຫຍາບຄາຍ. ການຖອດຊັ້ນຄວາມເສຍຫາຍຂອງພື້ນຜິວທີ່ປຸງແຕ່ງເປັນກຸນແຈໃນການປັບປຸງຄຸນນະພາບຂອງຫນ້າດິນຂອງ wafer. ຄວາມກວ້າງເຄິ່ງກວ້າງຂອງເສັ້ນໂຄ້ງ 4H-SiC (0004) ສາມາດກໍານົດລັກສະນະຄວາມເສຍຫາຍຂອງພື້ນຜິວຂອງ wafer ໄດ້ຢ່າງຖືກຕ້ອງແລະຊັດເຈນ.

ການຄົ້ນຄວ້າສະແດງໃຫ້ເຫັນວ່າຊັ້ນທີ່ເສຍຫາຍຢູ່ໃນຫນ້າດິນຂອງ wafers 4H-SiC ສາມາດຖືກໂຍກຍ້າຍອອກເທື່ອລະກ້າວໂດຍຜ່ານການປຸງແຕ່ງ wafer 4H-SiC, ປັບປຸງຄຸນນະພາບຫນ້າດິນຂອງ wafer ຢ່າງມີປະສິດທິຜົນ, ສະຫນອງການອ້າງອິງດ້ານວິຊາການສໍາລັບປະສິດທິພາບສູງ, ການສູນເສຍຕ່ໍາ, ແລະສູງ. ການປຸງແຕ່ງຄຸນນະພາບຂອງ wafers substrate 4H-SiC.

ເວລາປະກາດ: ກໍລະກົດ-08-2024