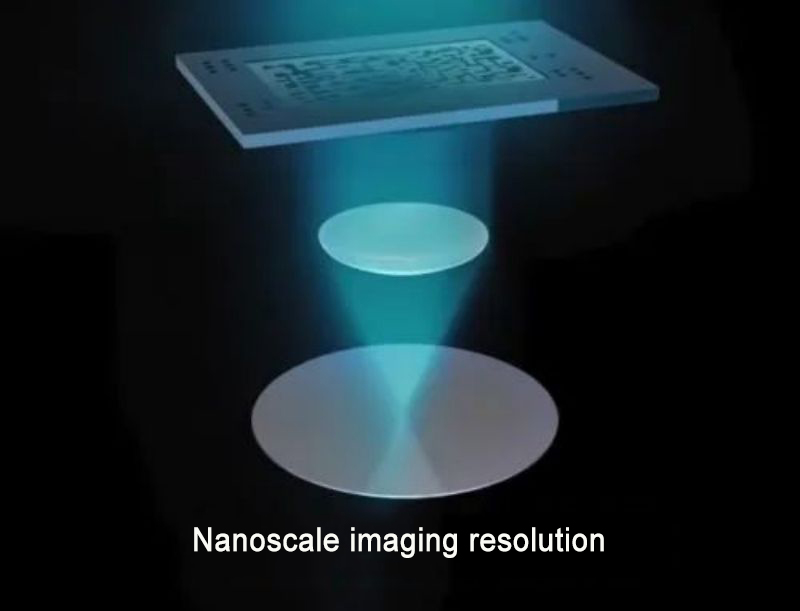

ຂອງຂະບວນການທັງຫມົດທີ່ກ່ຽວຂ້ອງກັບການສ້າງ chip, ຊະຕາກໍາສຸດທ້າຍຂອງwaferຈະຖືກຕັດເຂົ້າໄປໃນຕາຍຂອງບຸກຄົນແລະຫຸ້ມຫໍ່ຢູ່ໃນກ່ອງຂະຫນາດນ້ອຍ, ຫຸ້ມດ້ວຍ pins ຈໍານວນຫນ້ອຍທີ່ເປີດເຜີຍ. ຊິບຈະຖືກປະເມີນໂດຍອີງໃສ່ເກນ, ຄວາມຕ້ານທານ, ປະຈຸບັນ, ແລະຄ່າແຮງດັນ, ແຕ່ບໍ່ມີໃຜຈະພິຈາລະນາຮູບລັກສະນະຂອງມັນ. ໃນລະຫວ່າງຂະບວນການຜະລິດ, ພວກເຮົາຂັດ wafer ເລື້ອຍໆເພື່ອບັນລຸການວາງແຜນທີ່ຈໍາເປັນ, ໂດຍສະເພາະສໍາລັບແຕ່ລະຂັ້ນຕອນ photolithography. ໄດ້waferພື້ນຜິວຕ້ອງມີຄວາມຮາບພຽງທີ່ສຸດເພາະວ່າ, ໃນຂະນະທີ່ຂະບວນການຜະລິດຊິບຫຼຸດລົງ, ເລນຂອງເຄື່ອງ photolithography ຕ້ອງການບັນລຸຄວາມລະອຽດຂະຫນາດ nanometer ໂດຍການເພີ່ມຮູຮັບແສງຕົວເລກ (NA) ຂອງເລນ. ຢ່າງໃດກໍ່ຕາມ, ນີ້ພ້ອມກັນຫຼຸດຜ່ອນຄວາມເລິກຂອງຈຸດສຸມ (DoF). ຄວາມເລິກຂອງຈຸດສຸມຫມາຍເຖິງຄວາມເລິກທີ່ລະບົບ optical ສາມາດຮັກສາຈຸດສຸມ. ເພື່ອຮັບປະກັນວ່າຮູບພາບ photolithography ຍັງຄົງຈະແຈ້ງແລະຢູ່ໃນຈຸດສຸມ, ການປ່ຽນແປງດ້ານຂອງwaferຕ້ອງຕົກຢູ່ໃນຄວາມເລິກຂອງຈຸດສຸມ.

ໃນຄໍາສັບທີ່ງ່າຍດາຍ, ເຄື່ອງ photolithography ໄດ້ເສຍສະລະຄວາມສາມາດໃນການສຸມໃສ່ການປັບປຸງຄວາມແມ່ນຍໍາຂອງຮູບພາບ. ຍົກຕົວຢ່າງ, ເຄື່ອງ photolithography EUV ລຸ້ນ ໃໝ່ ມີຮູຮັບແສງຕົວເລກ 0.55, ແຕ່ຄວາມເລິກຕາມແນວຕັ້ງແມ່ນພຽງແຕ່ 45 nanometers, ມີຂອບເຂດການຖ່າຍຮູບທີ່ດີທີ່ສຸດທີ່ນ້ອຍກວ່າໃນລະຫວ່າງການຖ່າຍຮູບ. ຖ້າwaferບໍ່ຮາບພຽງ, ມີຄວາມຫນາບໍ່ສະຫມໍ່າສະເຫມີ, ຫຼືພື້ນຜິວ undulations, ມັນຈະເຮັດໃຫ້ເກີດບັນຫາໃນລະຫວ່າງການ photolithography ໃນຈຸດສູງແລະຕ່ໍາ.

Photolithography ບໍ່ແມ່ນຂະບວນການດຽວທີ່ຕ້ອງການກ້ຽງwaferດ້ານ. ຂະບວນການຜະລິດຊິບອື່ນໆຈໍານວນຫຼາຍຍັງຮຽກຮ້ອງໃຫ້ມີການຂັດ wafer. ສໍາລັບຕົວຢ່າງ, ຫຼັງຈາກການຂັດປຽກ, ການຂັດແມ່ນຈໍາເປັນເພື່ອເຮັດໃຫ້ພື້ນຜິວທີ່ຫຍາບຄາຍສໍາລັບການເຄືອບແລະການເຄືອບຕໍ່ມາ. ຫຼັງຈາກການແຍກຮ່ອງຮອຍຕື້ນ (STI), ການຂັດແມ່ນຕ້ອງການເພື່ອເຮັດໃຫ້ຊິລິໂຄນໄດອອກໄຊທີ່ເກີນແລະຕື່ມຂໍ້ມູນໃສ່ຂຸມ. ຫຼັງຈາກການຕົກແຕ່ງຂອງໂລຫະ, ການຂັດແມ່ນຈໍາເປັນເພື່ອເອົາຊັ້ນຂອງໂລຫະເກີນແລະປ້ອງກັນບໍ່ໃຫ້ການສັ້ນຂອງອຸປະກອນ.

ດັ່ງນັ້ນ, ການເກີດຂອງຊິບປະກອບດ້ວຍຂັ້ນຕອນການຂັດຈໍານວນຫລາຍເພື່ອຫຼຸດຜ່ອນຄວາມຫຍາບຄາຍຂອງ wafer ແລະການປ່ຽນແປງຂອງຫນ້າດິນແລະເອົາວັດສະດຸທີ່ເກີນອອກຈາກຫນ້າດິນ. ນອກຈາກນັ້ນ, ຄວາມຜິດປົກກະຕິຂອງພື້ນຜິວທີ່ເກີດຈາກບັນຫາຂະບວນການຕ່າງໆໃນ wafer ມັກຈະເຫັນໄດ້ຊັດເຈນຫຼັງຈາກແຕ່ລະຂັ້ນຕອນການຂັດ. ດັ່ງນັ້ນ, ວິສະວະກອນທີ່ຮັບຜິດຊອບສໍາລັບການຂັດແມ່ນຖືຄວາມຮັບຜິດຊອບທີ່ສໍາຄັນ. ພວກເຂົາເປັນຕົວເລກໃຈກາງໃນຂະບວນການຜະລິດຊິບແລະມັກຈະຮັບຜິດຊອບໃນກອງປະຊຸມການຜະລິດ. ພວກເຂົາເຈົ້າຈະຕ້ອງມີຄວາມຊໍານິຊໍານານໃນທັງສອງ etching ຊຸ່ມແລະຜົນຜະລິດທາງດ້ານຮ່າງກາຍ, ເປັນເຕັກນິກການຂັດຕົ້ນຕໍໃນການຜະລິດ chip.

ວິທີການຂັດ wafer ແມ່ນຫຍັງ?

ຂະບວນການຂັດສາມາດແບ່ງອອກເປັນສາມປະເພດໃຫຍ່ໂດຍອີງໃສ່ຫຼັກການປະຕິສໍາພັນລະຫວ່າງຂອງແຫຼວຂັດແລະຫນ້າດິນ wafer ຊິລິໂຄນ:

1. ວິທີການຂັດເຄື່ອງກົນ:

ການຂັດດ້ວຍກົນຈັກເອົາສ່ວນທີ່ຂັດຂອງພື້ນຜິວທີ່ຂັດອອກໂດຍຜ່ານການຕັດແລະການປ່ຽນຮູບຂອງພາດສະຕິກເພື່ອໃຫ້ໄດ້ພື້ນຜິວກ້ຽງ. ເຄື່ອງມືທົ່ວໄປລວມມີແກນນ້ໍາມັນ, ລໍ້ຂົນສັດ, ແລະເຈ້ຍຊາຍ, ການປະຕິບັດຕົ້ນຕໍດ້ວຍມື. ພາກສ່ວນພິເສດ, ເຊັ່ນ: ພື້ນຜິວຂອງອົງການຈັດຕັ້ງ rotating, ສາມາດນໍາໃຊ້ turntables ແລະເຄື່ອງມືຊ່ວຍອື່ນໆ. ສໍາລັບພື້ນຜິວທີ່ມີຄວາມຕ້ອງການທີ່ມີຄຸນນະພາບສູງ, ວິທີການຂັດລະອຽດສາມາດຖືກນໍາໃຊ້. ການຂັດຂັດທີ່ລະອຽດອ່ອນໃຊ້ເຄື່ອງມືຂັດທີ່ເຮັດເປັນພິເສດ, ເຊິ່ງໃນນໍ້າຂັດຂັດທີ່ມີສານຂັດ, ຖືກກົດດັນໃຫ້ແຫນ້ນກັບພື້ນຜິວຂອງວຽກ ແລະ ໝຸນດ້ວຍຄວາມໄວສູງ. ເຕັກນິກນີ້ສາມາດບັນລຸຄວາມຫຍາບຫນ້າຂອງRa0.008μm, ສູງທີ່ສຸດໃນບັນດາວິທີການຂັດທັງຫມົດ. ວິທີການນີ້ແມ່ນຖືກນໍາໃຊ້ທົ່ວໄປສໍາລັບການ mold ເລນ optical.

2. ວິທີການຂັດສານເຄມີ:

ການຂັດດ້ວຍສານເຄມີກ່ຽວຂ້ອງກັບການລະລາຍທີ່ມັກຂອງ micro-protrusions ເທິງພື້ນຜິວວັດສະດຸໃນອຸປະກອນທີ່ມີສານເຄມີ, ສົ່ງຜົນໃຫ້ພື້ນຜິວກ້ຽງ. ຂໍ້ໄດ້ປຽບຕົ້ນຕໍຂອງວິທີການນີ້ແມ່ນການຂາດຄວາມຕ້ອງການອຸປະກອນທີ່ຊັບຊ້ອນ, ຄວາມສາມາດໃນການຂັດຊິ້ນວຽກທີ່ມີຮູບຮ່າງທີ່ສັບສົນ, ແລະຄວາມສາມາດໃນການຂັດຫຼາຍ workpieces ພ້ອມໆກັນທີ່ມີປະສິດທິພາບສູງ. ບັນຫາຫຼັກຂອງການຂັດສານເຄມີແມ່ນການສ້າງຂອງແຫຼວຂັດ. ຄວາມຫຍາບຂອງພື້ນຜິວທີ່ບັນລຸໄດ້ໂດຍການຂັດສານເຄມີແມ່ນປົກກະຕິແລ້ວຫຼາຍສິບໄມໂຄແມັດ.

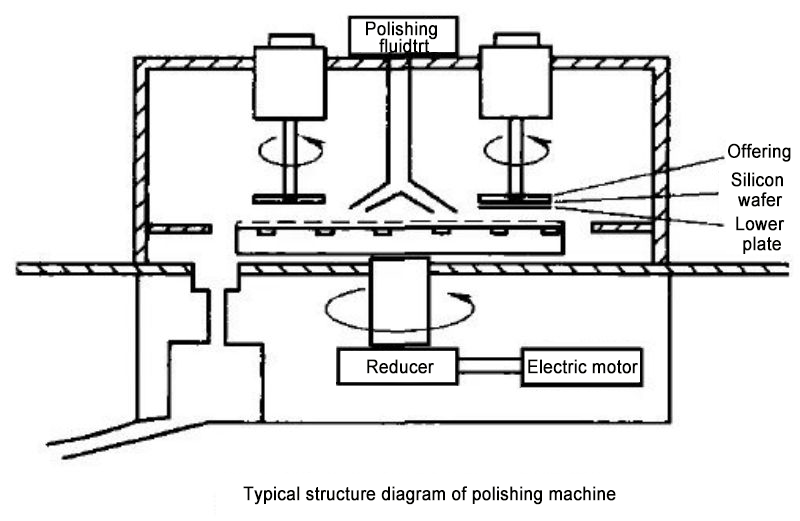

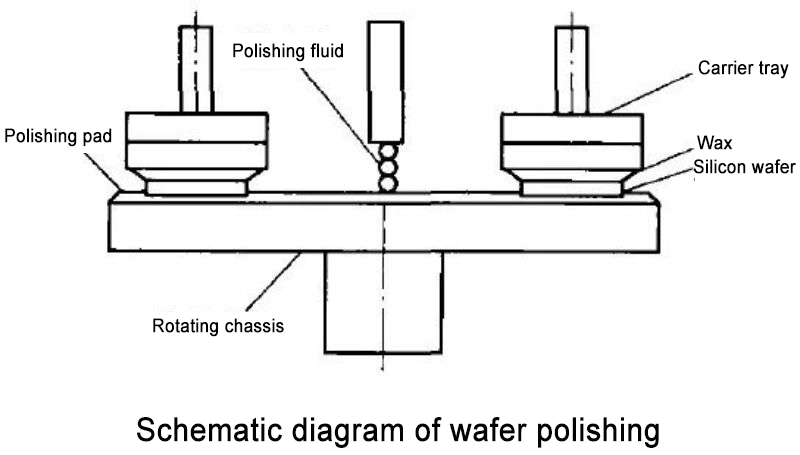

3. ວິທີການຂັດກົນຈັກເຄມີ (CMP):

ແຕ່ລະວິທີການຂັດສອງຄັ້ງທໍາອິດມີຂໍ້ດີທີ່ເປັນເອກະລັກຂອງມັນ. ການສົມທົບສອງວິທີນີ້ສາມາດບັນລຸຜົນກະທົບທີ່ສົມບູນໃນຂະບວນການ. ຂັດກົນຈັກເຄມີປະສົມປະສານ friction ກົນຈັກແລະຂະບວນການ corrosion ເຄມີ. ໃນລະຫວ່າງ CMP, ສານເຄມີໃນນໍ້າຂັດຂັດຈະອອກຊີເຈນຂອງວັດສະດຸຍ່ອຍທີ່ຂັດ, ປະກອບເປັນຊັ້ນຜຸພັງອ່ອນໆ. ຫຼັງຈາກນັ້ນ, ຊັ້ນ oxide ນີ້ໄດ້ຖືກໂຍກຍ້າຍອອກໂດຍຜ່ານການ friction ກົນຈັກ. ການເຮັດຊ້ໍາຂະບວນການ oxidation ແລະກົນໄກການໂຍກຍ້າຍນີ້ບັນລຸການຂັດປະສິດທິພາບ.

ສິ່ງທ້າທາຍໃນປັດຈຸບັນ ແລະບັນຫາໃນການຂັດເຄື່ອງກົນຈັກເຄມີ (CMP):

CMP ປະເຊີນກັບສິ່ງທ້າທາຍ ແລະບັນຫາຫຼາຍຢ່າງໃນຂົງເຂດເຕັກໂນໂລຊີ, ເສດຖະກິດ, ແລະຄວາມຍືນຍົງດ້ານສິ່ງແວດລ້ອມ:

1) ຄວາມສອດຄ່ອງຂອງຂະບວນການ: ການບັນລຸຄວາມສອດຄ່ອງສູງໃນຂະບວນການ CMP ຍັງຄົງເປັນສິ່ງທ້າທາຍ. ເຖິງແມ່ນວ່າຢູ່ໃນສາຍການຜະລິດດຽວກັນ, ການປ່ຽນແປງເລັກນ້ອຍໃນຕົວກໍານົດການຂະບວນການລະຫວ່າງ batches ຫຼືອຸປະກອນທີ່ແຕກຕ່າງກັນສາມາດສົ່ງຜົນກະທົບຕໍ່ຄວາມສອດຄ່ອງຂອງຜະລິດຕະພັນສຸດທ້າຍ.

2) ການປັບຕົວເຂົ້າກັບວັດສະດຸໃຫມ່: ໃນຂະນະທີ່ວັດສະດຸໃຫມ່ຍັງສືບຕໍ່ເກີດຂື້ນ, ເຕັກໂນໂລຢີ CMP ຕ້ອງປັບຕົວເຂົ້າກັບຄຸນລັກສະນະຂອງມັນ. ບາງວັດສະດຸຂັ້ນສູງອາດຈະບໍ່ເຂົ້າກັນໄດ້ກັບຂະບວນການ CMP ແບບດັ້ງເດີມ, ຮຽກຮ້ອງໃຫ້ມີການພັດທະນາຂອງແຫຼວຂັດແລະເຄື່ອງຂັດທີ່ປັບຕົວໄດ້ຫຼາຍຂຶ້ນ.

3) ຜົນກະທົບຂອງຂະຫນາດ: ໃນຂະນະທີ່ຂະຫນາດອຸປະກອນ semiconductor ສືບຕໍ່ຫຼຸດລົງ, ບັນຫາທີ່ເກີດຈາກຜົນກະທົບຂະຫນາດກາຍເປັນຄວາມສໍາຄັນຫຼາຍ. ຂະຫນາດນ້ອຍຕ້ອງການຄວາມຮາບພຽງຂອງຫນ້າດິນທີ່ສູງຂຶ້ນ, ຮຽກຮ້ອງໃຫ້ມີຂະບວນການ CMP ຊັດເຈນຫຼາຍກວ່າ.

4) ການຄວບຄຸມອັດຕາການໂຍກຍ້າຍວັດສະດຸ: ໃນບາງຄໍາຮ້ອງສະຫມັກ, ການຄວບຄຸມທີ່ຊັດເຈນຂອງອັດຕາການໂຍກຍ້າຍວັດສະດຸສໍາລັບວັດສະດຸທີ່ແຕກຕ່າງກັນແມ່ນສໍາຄັນ. ການຮັບປະກັນອັດຕາການໂຍກຍ້າຍທີ່ສອດຄ່ອງໃນທົ່ວຊັ້ນຕ່າງໆໃນລະຫວ່າງ CMP ເປັນສິ່ງຈໍາເປັນສໍາລັບການຜະລິດອຸປະກອນທີ່ມີປະສິດທິພາບສູງ.

5) ຄວາມເປັນມິດກັບສິ່ງແວດລ້ອມ: ນໍ້າຂັດ ແລະເຄື່ອງຂັດທີ່ໃຊ້ໃນ CMP ອາດມີສ່ວນປະກອບທີ່ເປັນອັນຕະລາຍຕໍ່ສິ່ງແວດລ້ອມ. ການຄົ້ນຄວ້າ ແລະ ການພັດທະນາຂະບວນການ ແລະ ວັດສະດຸ CMP ທີ່ເປັນມິດກັບສິ່ງແວດລ້ອມ ແລະ ຍືນຍົງ ແມ່ນສິ່ງທ້າທາຍທີ່ສຳຄັນ.

6) Intelligence and Automation: ໃນຂະນະທີ່ລະດັບຄວາມສະຫຼາດແລະອັດຕະໂນມັດຂອງລະບົບ CMP ຄ່ອຍໆປັບປຸງ, ພວກເຂົາຍັງຕ້ອງຮັບມືກັບສະພາບແວດລ້ອມການຜະລິດທີ່ສັບສົນແລະປ່ຽນແປງ. ການບັນລຸລະດັບອັດຕະໂນມັດທີ່ສູງຂຶ້ນແລະການຕິດຕາມອັດສະລິຍະເພື່ອປັບປຸງປະສິດທິພາບການຜະລິດແມ່ນສິ່ງທ້າທາຍທີ່ຕ້ອງໄດ້ຮັບການແກ້ໄຂ.

7) ການຄວບຄຸມຄ່າໃຊ້ຈ່າຍ: CMP ກ່ຽວຂ້ອງກັບອຸປະກອນແລະອຸປະກອນທີ່ສູງ. ຜູ້ຜະລິດຕ້ອງປັບປຸງການປະຕິບັດຂະບວນການໃນຂະນະທີ່ພະຍາຍາມຫຼຸດຜ່ອນຄ່າໃຊ້ຈ່າຍໃນການຜະລິດເພື່ອຮັກສາຄວາມສາມາດໃນການແຂ່ງຂັນຂອງຕະຫຼາດ.

ເວລາປະກາດ: 05-05-2024